探秘Chiplet与先进封装

作者|CH_TrialBlazers 来源|CEIA电子智造(ID:sciencenet-cas)

各位CEIA电子智造的朋友们,大家好,我是B站UP主CH,今天我们来聊聊Chiplet与先进封装。

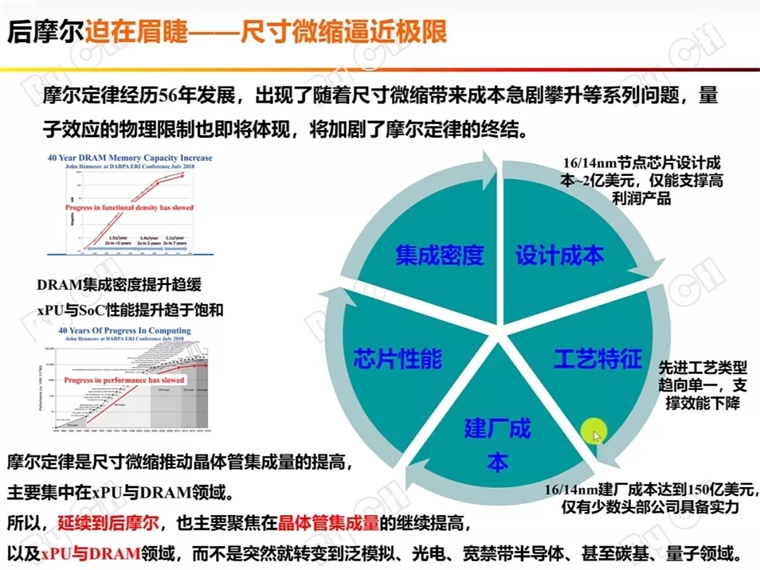

摩尔定律经过56年的发展,出现了随着尺寸微缩而带来的成本急剧攀升等一系列问题。越来越贵、越来越少这样的特征让量子效应的物理限制也即将开始体现,这些将加剧摩尔定律的终结。像16/14纳米节点芯片的设计成本已经高达2亿多美元,具备这样设计能力的公司也只能支撑高利润的产品,那先进工艺类型也开始趋向于单一,支撑的效能开始下降。16/14纳米建厂的成本已经达到了150亿美元,只有一些少数的头部公司才具备相关的实力。DRAM的集成密度的提升也开始趋缓,处理器和SOC性能的提升也趋于饱和,这些都开始跟不上摩尔定律的预测,所以后摩尔迫在眉睫,尺寸的微缩开始逼近了极限。

摩尔定律主要是靠尺寸的微缩来提高晶体管的集成量,主要是集中在处理器和DRAM领域,也是一些高利润的产品。所以如果延续到后摩尔,也主要聚焦在晶体管提成量的继续提高以及处理器和DRAM领域,而不是突然地就会转变到泛模拟、光电、宽禁带半导体甚至碳基、量子领域,所以有一些宣传其实有一定的误解。如果我们只是提从摩尔定律到后摩尔,其实是在延续之前在处理器、DRAM的集成度,而不是转变到其它的领域。

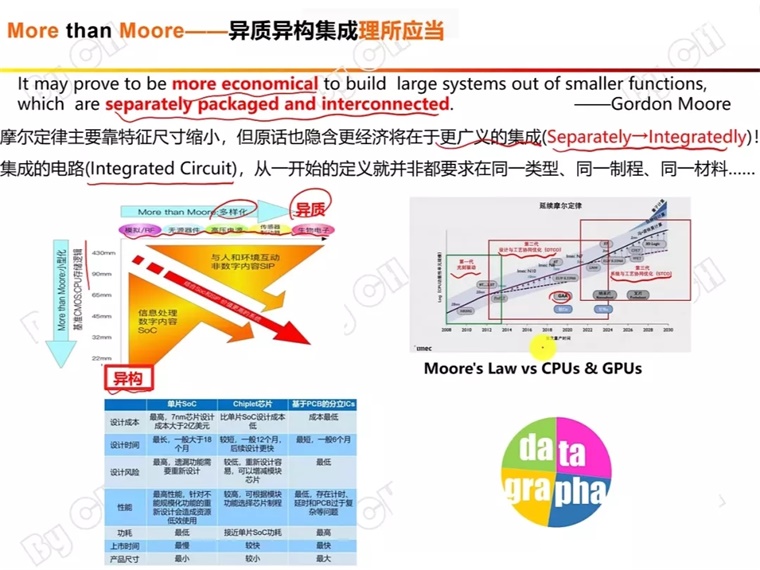

我们需要比尺寸微缩更多的一些技术手段和衡量方式,即More Than Moore,其中异质异构集成首当其冲、理所应当。这个视频是一个关于摩尔定律它所预测的集成晶体管的数量与当时最先进的CPU或者GPU所集成晶体管数量的一个对比。最早是英特尔的4004比较具有代表性,到后来像一些GPU它的集成晶体管数量开始变多,甚至有一些超过了当时最领先的CPU,摩尔定律才是驱动我们在通用逻辑芯片上不断去集成更多的晶体管的一个推动力。

这个视频它的一个产品的统计是截止到2019年,后续也有可能会有与摩尔定律所匹配的一些通用逻辑芯片产品,包括CPU或者GPU,但是随着尺寸微缩已经到了5、3纳米甚至更低,我们不可能无限制地尺寸微缩下去,所以我们只需要其它的技术手段能去集成更多的一些晶体管。

戈登摩尔在阐述摩尔定律的原话里包括的内容还是很多的,其中有这么一句话,它提到了一个很关键的、我们现在比较忽视的,就是更加经济,最早更加经济,可能是把一些数字芯片做得集成度越来越大,再对不同功能的芯片进行封装和互联这样所构成的系统。

所以摩尔定律主要是靠尺寸微缩,这个原话里可能也隐含着更加经济,在当时的未来可能意味着更广义的集成,如果我们对原话进行稍加改动的话,集成电路它的英文是Integrated Circuit,其实从这个定义上来讲,就并非要求是在同一个类型、同一个制程或者是同一个材料。

More Than Moore异构异质集成主要是从两个方面,一个是我们要针对逻辑芯片和存储器,在More Moore的基础上用异构集成来进行替代,这样是为了集成更多的晶体管。另外还有就是去集成更多的泛模拟的器件,甚至非半导体的器件来进行异质集成。为了多样化,这样它包括的功能可能会更丰富。那IMEC也在延续摩尔定律的路线图里提到了很多的未来有可能的技术手段,现在我们还是处于一个光刻来驱动尺寸微缩的时代,后续我们可能会进入设计与工艺协同优化以及系统与工艺协同优化的阶段。

里面也提到了很多像尺寸继续微缩的GAA,像3D Logic 3D堆叠的逻辑芯片,在实际产品上目前也出现了很多Chiplet的异构芯片,它与单片的SoC或与基于PCB的分离的ICs相比较,也是综合了双方的各自优势,特别是在成本和性能上面。

异质异构集成它的一个基本的部件就是Chiplet,最终形成的是一个广义的SiP大芯片。下面是一个关于这方面的科普介绍,比如我们一开始是同构同质的基于各类IP的SoC,不能同质同构的各类IP,我们就把它芯片换到了Chiplet,这样SoC就变成了包括更多功能的SiP。

我们可以利用硅基的各个制程上的优势,在每个Chiplet上有不同的制程,比如7纳米、10纳米、28纳米甚至45纳米以及更多,这样的话我们可以去集成逻辑、存储、接口甚至一些模拟电路。另外我们还可以引入更多的材料形成异质,即除了硅以外,还可以集成氮化钾、碳化硅、磷化铟,这些是为了集成射频、功率以及光电等一些应用需求,这些都是一个水平的互联,我们还可以向上垂直堆叠,一般硅类IC较多,故所要求堆叠的程度会比其它的要高,那理想化的话就是形成一个广义的SiP的大芯片,会包括了逻辑存储以及泛模拟甚至传感器。

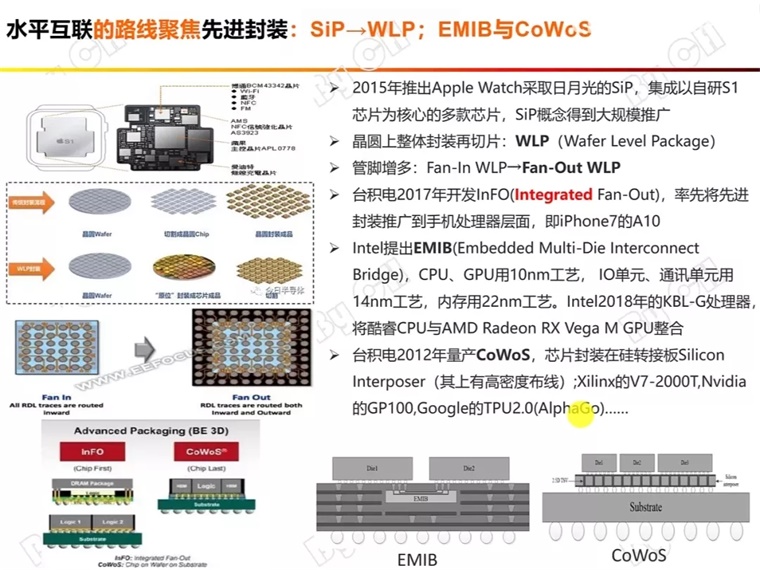

我们把水平互联和垂直堆叠分开来看,水平互联的路线主要是聚焦在先进封装上,像2015年苹果推出的第一代iWatch,就采取了日月光的SiP先进封装,集成了以它们自研的S1芯片为核心的多款芯片,整体它也叫一个S1的模块,SiP的概念也得到了一个大规模的推广。另外也出现了晶圆级封装,传统的封装流程是先切割再整体封装,晶圆级封装是先在原位上整体封装、再进行切割,后来也出现了扇出型的晶圆级封装,这样可以增添很多的管脚。

台积电在2017年开发了Info技术,集成的扇出封装,率先将先进封装推广到了手机处理器的层面及iPhone7的A10。

英特尔也提出了EMIB的先进封装,在CPU、GPU上用10纳米的工艺在IO单元、通信单元用14纳米工艺在内存上用22纳米工艺,在18年做出了一个处理器产品,将酷睿CPU和AMD的GPU进行了整合,比较有划时代意义的一个产品。

台积电是在2012年就开始量产了先进封装技术,也是支撑了Xilinx的V7产品,因为拿到GP100,谷歌的TPU2.0等等Fabless的先进产品,为它们的性能提升也提供了很多的帮助。

垂直堆叠的思路最早源于存储,像三星最早做出了3D NAND Flash的结构,到现在3D NAND Flash最高已经可以到了176层,后来转移向了DRAM,DRAM的堆叠主要是为了解决和处理器的高速互联的问题,三家DRAM厂家也均有DRAM堆叠的产品,它们也都是和处理器厂家一块合作推出的。再到台积电它的先进封装显示也是支持DRAM的堆叠。

然后就是逻辑芯片的3D,英特尔有推出Foveros 3D Chiplet技术,最近长电也发布了它们在Chiplet上的一个技术的集成,里边包括了2D、2.5D以及3D。在它的3D Chiplet里面有提到是face to face的一个堆叠,我们可以看到英特尔它的Foveros也是face to face的堆叠,如果我们把一个Die裸芯具有焊点的这一面,看看它的face面的话,另外一面就是它的背面back这一面。

所以我们可以看到不论是Fovero还是长电的3D Chiplet,都是face to face的封装形式,这种情况下它的堆叠就不可能无限制的向上累加,像3D NAND或者右边的DRAM这种比较多层的堆叠。

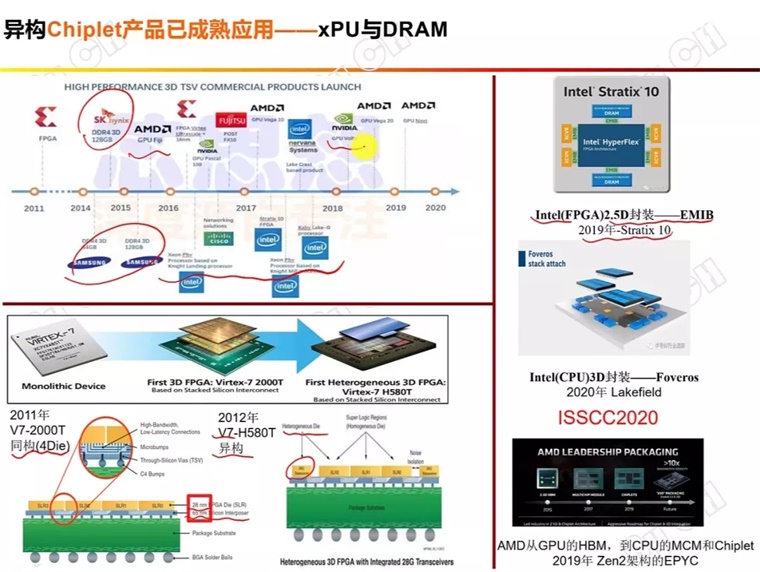

主线是摩尔定律和后摩尔,所以我们先重点的关注一些异构的Chiplet产品。它们在这些年也已经成熟地应用在了处理器和DRAM领域,最早应该是Xilinx和台积电合作的FPGA。在2011年推出的V7是四个同构的裸芯是在28纳米的制程上,它们是堆在了65纳米的硅转接板上。在2012年它们又合作推出了异构的V7,除了逻辑单元以外,它们还在硅转接板上堆了收发器,应该这是一个真正意义上第一款的异构Chiplet通用逻辑大芯片。我们知道FPGA还有另外一大厂家,就是收购的Altera的英特尔与台资电所竞争的2.5D封装是EMIB技术,在2019年推出了一款FPGA的产品,就是采取EMIB技术进行异构集成。

前面我们也提到,最早是3D NAND Flash,然后就是DRAM,之后就是一些逻辑器件,包括CPU、GPU等等。可以说一些知名的逻辑芯片厂家基本上都在推出自己的异构Chiplet的产品,还有两家在CPU上竞争的英特尔和AMD。像英特尔推出的Lake field,AMD之前推出基于DRAM堆叠技术的GPU,也有近些年推出的Zen架构的霄龙处理器,所以异构集成应该成为了各个存储器和逻辑芯片厂家的共识,特别是在后摩尔时代。

这边举这4个代表性芯片是有一定的用意的,我们可以思考一下。一方面前面提到过英伟达也补上了CPU部分,AMD谋求并购Xilinx补上FPGA,也都是在紧跟后摩尔的异构时代变化。那英特尔可能很早就意识到,所以才既收购了Altera补充产品线种类,又一直不肯放弃后端产业链,寻求设计工艺协同优化,早早就表现出对尺寸微缩的信息丧失,很早就布局异构时代。

但另一方面,在前些年尺寸微缩还远没到尽头,Fabless+Foundry的模式引领着尺寸微缩,促进Xilinx和AMD狠狠地打击了英特尔的FPGA和CPU。特别是Xilinx推出ACAP,既解决对开发者的编程不友好,又发挥可定义硬件的自适应优势,所以英特尔很早就布局异构时代,在战略上貌似成功,反而由于研发精力的分散而丧失了很多技术优势。

这类似于之前的摩托罗拉铱星计划,计划是很好,但在当时还没有到那个时代,现在终于也有了Space X的星链计划,那想表达的意思还是要脚踏实地地做,而不是觉着一眼看到很远的时代,就不去踏实解决眼前的问题。因为市场上还是有竞争者在十分努力地提升自己,战略上布局的成功,并不意味着商业上真正意义的成功。

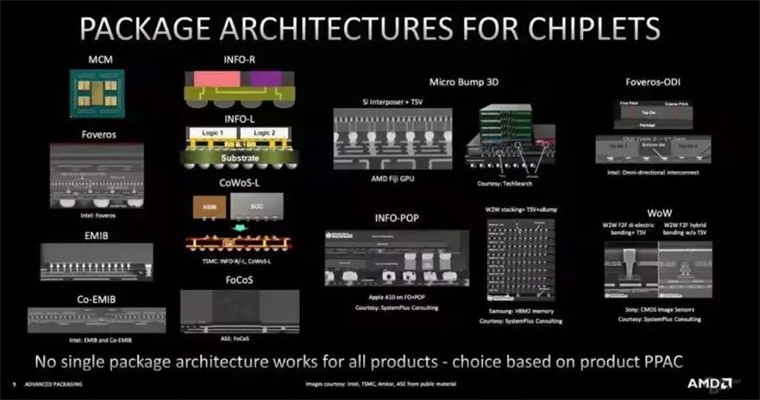

AMD在最近的hot Chips会议上,有对Chiplet的各类技术进行了总结,包括了刚刚我们所讲的各种也表达了Chiplet仍然类似于处理器与ASIC各类存储器或者各类指令集等等半导体的其它领域,是术业有专攻的,是各有侧重的,而不要只想着某一个Chiplet的方式便可以一招鲜,这也就是设计工艺协同优化的体现。前面也提到过PPA,即功率、性能、面积之间的Trade-off权衡,这里它也提到了一个C,就是成本。今天的课程分享到这里就结束了。感谢CEIA电子智造提供的平台,同时我在B站上开设了自己的个人账号,欢迎大家多来看看,开展交流,谢谢。

本文来源于B站UP主CH_TrialBlazers,他就Chiplet及半导体先进封装技术开展了相关讨论,版权归属于作者本人及CEIA电子智造所有。

编者按:本文转载自微信公众号:CEIA电子智造(ID:sciencenet-cas)

广告、内容合作请点这里:寻求合作

咨询·服务