Chiplet,后摩尔时代国产芯片弯道超车的机会?

t图源:摄图网

作者|关注硬件的 来源|奇偶派(ID:jioupai)

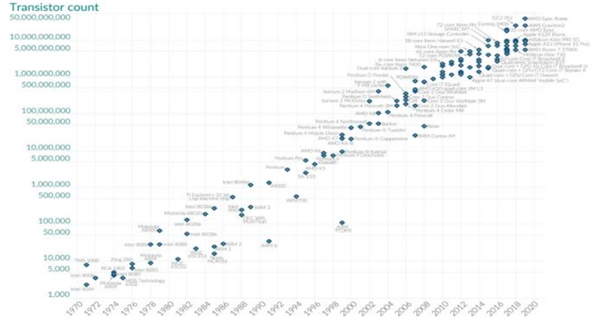

2023年3月24日,半导体行业先驱、英特尔联合创始人、“摩尔定律”提出者戈登·摩尔在他夏威夷的家中去世,享年94岁。伴随着戈登·摩尔的去世,似乎他提出的摩尔定律也正在逐渐成为历史长河中的一个名词。

而现实也似乎确实如此,近年来,伴随着半导体行业的制程工艺即将逼近物理极限,带来的就是每一代晶体管密度的增速在放缓,芯片主频的提升速度更慢,性能的改善越来越难。

这一切的现实,看起来都在印证一件事——摩尔定律正逐渐迈向最后极限。

也正是在这样的背景下,英伟达的创始人、CEO黄仁勋表示,以类似成本实现两倍业绩预期对于芯片行业来说已成为过去,“简而言之,摩尔定律已经死了。”

但是,也有科技巨头并不这么认为,在Intel Innovation 2022的开幕活动上,英特尔现任CEO帕特·基辛格声嘶力竭地表示,“摩尔定律”没有死,它还活得好好的。

而与英特尔持有同样态度的,还有英伟达的老对手AMD。最近,苏姿丰在接受《巴伦周刊》的采访中,她明确地表示,摩尔定律当前并未消亡,只是有所放缓,当前我们需要采取不同的方式来克服性能、效率和成本上的挑战。

她提到:“晶体管成本的增加、密度提高带来的改进,每一代的综合性能提升可能都不大,但我们通过不断地更迭,一步一步地向前迈进。我们今天在 3nm 方面做了很多工作,也在研究 2nm,将继续使用 Chiplet 这类结构来绕过摩尔定律的一些挑战。”

那么,为什么说黄仁勋认为摩尔定律已经死了?为什么英特尔、AMD、台积电等巨头却因Chiplet技术而信心满满?在3nm工艺良率不高、1nm及以下工艺尚不明朗的情况下,Chiplet又是怎样掀起一场架构创新层面的革命?对我国被卡脖子的芯片企业又有多大的帮助呢?

本文将以Chiplet走到台前的原因,国际各大厂商应用状况,国内受益产业链及相关公司的顺序展开,以期为读者展现新技术的发展状况及投资机会。

1

Chiplet 走到台前,是一种必然

从1987年的1um制程到2015年的14nm制程的发展历程中,集成电路制程的迭代大致符合“摩尔定律”的规律,随着工艺进步,集成电路上晶体管密度不断提升,驱动计算机性能保持几何级数增长,而性能的快速提升也推动了芯片价格迅速下降。

但自2015年以来,集成电路先进制程的发展开始放缓,7nm、5nm、3nm制程的量产进度均落后于预期。

而随着台积电宣布2nm制程工艺实现突破,量子物理的影响也逐渐显著了起来,现有集成电路制程工艺已经接近了物理尺寸的极限,因此很难进一步往前推进,摩尔定律发展陷入瓶颈,行业也正式进入了“后摩尔时代”。

资料来源:AMD

而在量子物理效应极大地制约了摩尔定律的正常延续外,先进制程推进所带来的经济效益也正在锐减。

根据IBS报告,以全球某领先智能手机公司为例,其晶体管的生产成本在16nm工艺节点下为每10亿个晶体管4.98美元,而7nm工艺节点下为2.65美元。但是整体来说,摩尔定律持续推进所带来的成本下降正在逐步放缓,并逐渐难以覆盖昂贵研发成本的投入。

那么,在摩尔定律的经济效益快速降低、先进制程难以突破物理极限的情况下,集成电路产业就只能止步不前了吗?

答案自然是否,在先进制程之外,先进封装与架构创新同样能够在一定程度上弥补先进制程的缺失,使用面积和芯片的堆叠来换取算力和性能,而这就需要引入系统级别的新设计理念,而Chiplet便是其中之一。

作为先进封装技术的代表,Chiplet走向了和传统SoC完全不同的道路。

随着对芯片性能的要求日益提高,传统单片SoC变得太大且成本过高,良率风险也逐渐攀升。在此背景下,集成电路产业开始思考将不同工艺的模块化芯片进行组合封装。

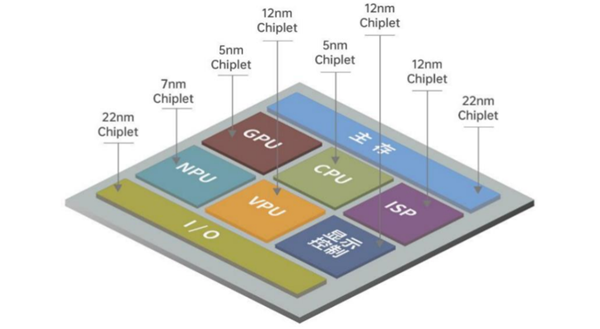

Chiplet将复杂SoC芯片拆解成一组具有单独功能的小芯片单元die(裸片),通过die-to-die将模块芯片和底层基础芯片封装组合在一起,可以降低成本,减少浪费,并大大改善可靠性。

而其底层的实现原理与搭积木相仿,从设计时就按照不同的计算单元或功能单元对其进行分解,然后每个单元选择最适合的工艺制程进行制造,再将这些模块化的裸片互联起来,通过先进封装技术,将不同功能、不同工艺制造的Chiplet封装成一个系统芯片,以实现一种新形式的IP复用。

资料来源:芯原股份公告

与传统的SoC相比,Chiplet在设计灵活度、设计与生产成本、上市周期等方面有着明显的优势。

首先,Chiplet在很大程度上降低芯片设计的复杂程度,有效降低研发与设计成本。

Chiplet芯粒设计灵活,且可重复使用,可以仅对芯片上的部分单元进行选择性选代,即可制作出下一代产品,加速产品上市周期。并且,Chiplet通过采用已知合格裸片进行组合,也能有效缩短芯片的研发周期及节省研发投入。

据悉,设计28nm芯片的平均成本为 4000 万美元,设计 7nm 芯片的成本上升至 2.17 亿美元。而The Linley Group的白皮书中提出,Chiplet技术可以将大型7nm设计的成本降低 25%。

资料来源:英特尔,中航证券研究所

其次,Chiplet能够显著提高大型芯片的良率,降本增效。

传统的SoC将多个不同类型计算任务的计算单元以光刻形式集成在同一片晶圆上,随着先进制程不断推进,单位面积上集成的晶体管数量越来越多,芯片生产中的工艺误差和加工缺陷显得愈发明显,也对制造过程中的芯片良率提出较高挑战,因为一个微小的缺陷就可能导致整个大芯片报废。

而Chiplet方案则通过将大芯片分成更小的芯片的方法,将单一裸片面积做小,这样就算有缺陷出现,也只会导致缺陷所在位置的小芯片报废,而不会导致整个芯片无法使用,有效地提高了芯片的良率。

资料来源:英特尔,中航证券研究所

最后,Chiplet还可以通过更加更加合适的制程选择大幅降低芯片制造成本,缩短上市周期。

传统SoC中的每个逻辑计算单元对性能要求都很高,整体依赖先进制程,具有极高的生产壁垒与制造成本;Chiplet 方案则可针对不同的模块采取不同合适的制程,分别进行制造或是对外进行采购,最后采用先进的封装技术进行组装,将相对落后制程的芯片与先进制程的芯片相组合,大幅降低了芯片的制造成本。

此外,还可以对不同芯片进行分别选择性地迭代,而迭代部分裸芯片后便可制作出下一代产品,大幅缩短产品上市周期。

进入后摩尔时代,SoC开始在供电、功耗和散热等方面力有不逮、设计生产全流程成本大幅增加、制程工艺接近极限之时,Chiplet 作为当下较最关注的半导体发展方向之一,能够有效降低能够有效降低芯片设计与制造的门槛,或将成为未来十数年中下提升芯片集成度与算力的重要途径。

2

苹果华为英特尔AMD

力推Chiplet产品化落地

在如此多的优势之下,Chiplet自然得到了众多国际巨头的青睐,而Chiplet技术的内部,也分为了两大技术门派。

一类是基于功能划分到多个Chiplets,而每个Chiplet不包含完整功能集合,而是通过不同Chiplets组合封装实现不同类型的产品,其中的主流代表有华为的Huawei Lego架构与超威半导体的AMD Zen2/3架构。

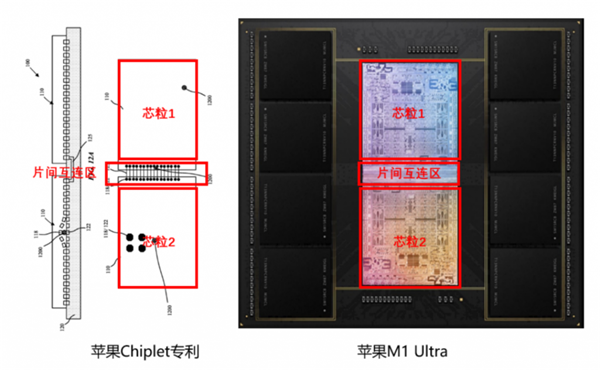

而另一类则是每个Chiplet中都包含较为独立完整的功能集合,通过多个Chiplets级联来获得性能的线性增长,其中的主流代表有苹果的Apple M1 Ultra和英特尔的Intel Sapphire Rapids。

其中,AMD作为引领Chiplet风潮、产品化进度最快的厂商,其自2019年的Zen 2架构便开始采用Chiplet技术,基于Zen 2架构的产品在单/多核处理能力上均有很大提升,能耗比改善明显。

使用了Chiplet技术的第二代霄龙处理器与第一代相比,核数增加了100%,晶体管数增加了102%至380亿,而硅片面积仅增加了18%,这充分显示了7nm制程下高密度优势。此外,第二代的整数和浮点运算性能也分别提升了144%和97%。

此后,AMD也联手台积电,借助台积电先进的封装工艺,共同推出了3D Chiplet产品,并于2022年推出了 RDNA3 架构的 7000 系显卡,而这也是史上第一款采用Chiplet技术的 GPU。

在3D Chiplet技术的支撑下,AMD产品的竞争力逐渐提升,近两年来,AMD旗舰CPU、GPU的性能不断提升,虽然与英特尔相比仍有所欠缺,但市场中已经基本形成了两大寡头竞争的局面。

同时,AMD旗下含Chiplet技术的CPU产品销量占比不断提高,在2021年10月至2022年12月间,从约80%上升至97%,让AMD成为了Chiplet技术当之无愧的代言人。

而在AMD之外,英特尔基于IDM优势,也积累了较为完整的互连技术优势。

基于IDM的制造优势,英特尔开发了EMIB(全方位互连硅桥)和Foveros两种封装技术,分别对应横向和纵向之间的连接。英特尔FPGA芯片Stratix 10最早采用了EMIB支持的Chiplet技术。

2023年,英特尔基于Chiplet技术发布了第四代至强可扩展处理器和至强CPU Max,以及数据中心GPU Max。

资料来源:英特尔官网

至强CPU Max拥有56个性能核,内核的4个小芯片使用EMIB连接,进行自然语言处理时高带宽内存优势可提升20倍性能。而数据中心GPU Max是英特尔针对高性能计算加速设计的第一款GPU产品,一个封装中有超过1000亿个晶体管,拥有47个不同的块和高达128GB的内存。

在主攻PC端的厂商之外,苹果也采用了UltraFusion的架构,成功实现高速互连。

2022年3月,苹果推出的M1 Ultra芯片,又一次触动了芯片界的游戏规则。该是迄今为止苹果最强大的芯片,尽管很多计算芯片已采用Chiplet技术提升性能,但苹果的“拼装货” M1 Ultra却还是让PC界震撼。

M1 Ultra 支持高达 128GB 的高带宽、低延迟统一内存,支持 20 个CPU核心、64个GPU核心和32核神经网络引擎,每秒可运行高达 22 万亿次运算,提供的 GPU性能是苹果M1芯片的 8 倍,提供的GPU性能比最新的 16 核 PC 台式机还高 90%,而达到峰值性能时的功耗则要低100瓦。

而根据M1 Ultra发布的UltraFusion图示,以及苹果及其代工厂台积电的公开专利和论文来看,本次M1 Ultra芯片的UltraFusion架构,应是基于台积电第五代CoWoS Chiplet技术的互连架构,也正是台积电在Chiplet技术中拥有如此先进的制造、封装工艺,才得以实现苹果的新架构,进而震撼业界。

可以毫不夸张地说,正是因为各大厂商不断进行的Chiplet架构领域的研究,还有以台积电为代表等厂商持续推制造工艺,才让近年来硬件圈仍能保持较快的发展速度,而未来对Chiplet的研究,也将继续推进下去。

3

Chiplet,通富微电和芯原股份的机会?

在国际巨头们纷纷入局的情况下,国内自然也有所涉足,但对于我国来说,Chiplet不仅仅意味着尖端技术的推进,还意味着国产现有半导体制造能力的提升。

我们在与华为负责先进封测核心技术的部门研发总监的交流中,对方表示,对于中国半导体产业来说,Chiplet技术是在短期内最有机会破局先进制程限制的路线。但虽然相当于换到了一个新的赛道,有了更多的机会,但整体上来说国内仍然需要加速追赶,其中封装作为最有机会的产业链环节,涌现了众多优秀的国产厂商与投资机会。

先进封装技术是Chiplet 实施的基础和前提,而近年来我国封测行业稳步发展,快速成长。

目前我国集成电路领域整体国产自给率较低,尤其是半导体设备、材料与晶圆制造等环节,与国际领先水平差距较大,而封测为我国集成电路领域最具国际竞争力的环节,2022年,中国大陆有4家企业进入全球封测厂商前十名,分别为长电科技、通富微电、华天科技和智路封测。

而其中,通富微电作为深度绑定AMD的厂商,近年来业绩快速增长。

通富微电主要提供集成电路设计仿真,圆片中测,封装,成品测试,系统级测试等一站式服务,在2022的全球封测厂商中排名第五。公司封装类型齐全,涵盖框架类封装、基板类封装、晶圆级封装及COG、COF和SIP等,可以应用于众多消费、使用场景。

而得益于技术的领先, 通富微电目前已与AMD、英飞凌、意法半导体、联发科、长江存储等国内外细分领域头部厂商建立了长期稳定的合作关系。而作为深度绑定AMD的封测厂商,通富微电的业绩,也伴随AMD崛起快速增长。

根据与通富微电相关人士的交流,奇偶派得知AMD GPU 80%都是由通富微电来进行封测,AMD全系列产品占到了公司收入的五成之上。

通富微电于2016年成功收购了AMD苏州及AMD马来西亚槟城各85%股权,与AMD形成了“合资+合作”的强强联合模式,在深度锁定了AMD供应链并占据AMD封测订单大部分份额的同时,积极承接国内外客户高端产品的封测业务,进一步增强了公司业绩确定性。

通富微电营收图

资料来源:choice,东方财富证券研究所

而在Chiplet技术方面,通富微电提前进行了2.5D/3D等先进封装技术布局,公司目前已建成国内顶级超大尺寸FCBGA 研发平台与2.5D/3D封装平台,各项技术布局进展顺利。

目前,已经开始大规模生产Chiplet产品,工艺节点方面,7nm产品成功实现量产,5nm产品也完成了研发,进入量产前夕, 随着AMD采用Chiplet技术的新产品陆续发布,公司有望充分受益。

而在封测之外,上游的半导体IP在IC设计中,也起着不可或缺的作用。

半导体IP是指集成电路设计中预先设计、验证好的功能模块,位于IC设计上游,提供SoC所需的核心功能模块,该环节拥有技术密集度高、知识产权集中、商业价值昂贵等特征,是集成电路设计产业的核心产业要素和竞争力体现。

Chiplet则开启了新型IP复用模式,将硅片级别的IP进行复用,大大降低了开发时间、提高了产品良率与重复使用率,同时也给予了芯片IP公司新的发展机遇。

而在国内,芯原股份作为业内的佼佼者,或将借Chiplet技术快速发展。

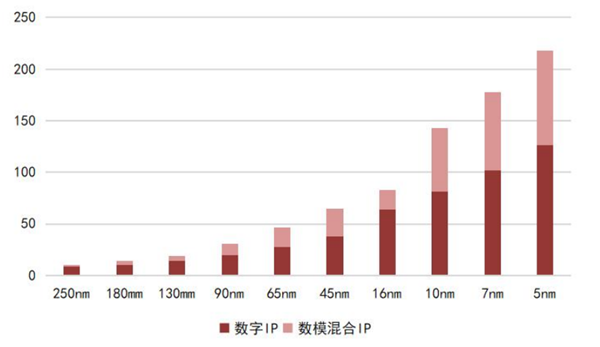

芯原股份是国内领先的一站式芯片定制服务和半导体IP授权服务企业,在全球半导体IP授权供应商中排名第七,而IP种类与成长率在全球前七中排名均为前二。

芯原有六大核心处理器IP,分别为图形处理器IP、神经网络处理器IP、视频处理器IP、数字信号处理器IP、图像信号处理器IP和显示处理器IP,此外还有1400多个数模混合IP和射频IP。

芯原股份IP数量示意图

资料来源:芯原股份招股说明书,东莞证券研究所

而在Chiplet领域的探索上,芯原股份在极早期便前瞻性布局IP芯片化,目前公司已经推出了基于Chiplet架构所设计的高端应用处理器平台,该平台12nm SoC版本已完成流片和验证,并正在进行Chiplet版本的迭代。

此外,芯原还是中国大陆首个加入UCIe产业联盟的企业,也意味着受到了国际Chiplet“联盟”的认可。未来,利用Chiplet技术进行IP芯片化有望让公司充分受益于尖端技术发展,带来全新商业模式。

4

写在最后

进入后摩尔时代后,当先进制程难以推动硬件设备快速发展之时,Chiplet技术已经成为半导体行业的重要发展趋势之一。据研究机构Omdia数据显示,全球Chiplet处理器芯片市场规模预计到2024年达58亿美元,而到2035年将突破570亿美元。

而对于国内来说,在先进制程发展被封锁,难以快速推进的情况下,Chiplet也为国产替代开辟了新思路,有望提升中国集成电路产业综合竞争力,成为我国集成电路产业逆境中的突破口之一。

而在这个产业发展叠加封锁突破的大背景下,国内相关产业链也将迎来价值重塑,产业链中的相关公司本就实力充足,也必会在本次更换赛道的发展中跻身国际龙头,寻找到新的业绩增长空间。

参考资料:

1.《后摩尔时代新星,Chiplet与先进封装风云际会》,中航证券;

2.《Chiplet与先进封装共塑后摩尔时代半导体产业链新格局》,东方财富证券;

3.《Chiplet助力半导体产业弯道超车,先进封装、IC载板、半导体IP等多环节受益》,东莞证券;

4.《Chiplet如何助力AI芯片算力跨越》,民生证券;

编者按:本文转载自微信公众号:奇偶派(ID:jioupai),作者:关注硬件的

广告、内容合作请点这里:寻求合作

咨询·服务